const int *p说明不能修改_C++ const详解

常量在C++中经常用到,用关键字const表示,它是常数变量,也就是说,它仍然是变量,而不是常数。什么区别呢?编译器会为变量在内存中分配地址空间,而常数是编译器在编译过程中记录在内存表里一个实体。

常量定义

const int a = 10;

在定义完之后,就不能再修改常量a的值了。如果是在不同的文件中使用,需要用到关键字extern

extern const int a ;

这样表示变量a是一个定义别处的全局变量,在这里只能使用,并不能修改,但a并不一定真的是一个const。

指针常量和常量指针

这应该是C++面试和笔试中经常考到的一个知识点。

指针常量

int const q = 10; // q is const q = 20; // OK

q++; // ERROR

指针常量,在上面的代码中,q是常量,指向的地址是不能变化的,但指向地址中的内容是可以改变的。

常量指针

int a = 10;

int b = 20;

const int p = &a; // p is const

*p = 15; // ERROR

a = 30; // OK

p = &b; // OK

常量指针,在上面的例子中,(p)是常量,我们不能通过(p)来改变指向的对象即a;但a本身是可以改变的,而且p也是可以指向别处的。

有什么好办法容易区分这两个呢?可以看const和*的先后顺序:

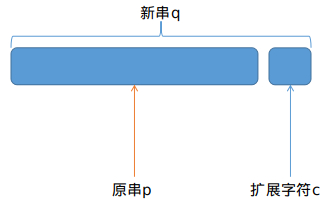

const int *p; //常量指针int *const p; // 指针常量

而且只要我们记住,const后面的是常量,这样就很容易区分它们的功能,对于常量指针,*p都在const后面,所以*p是个常量,直接对*p赋值的操作肯定是错误的;而指针常量,只有p在const后面,所以p是常量,指针指向地址是不能变的,但指向地址里面的内容是可以变的。

函数参数中的常量

如果函数的参数中有常量,那么在函数中,该参数是不能被修改的

int func(const int i){i++; // ERROR}

函数返回值为常量

int f1() {return 1;}const int f2() {return 1;}int main(){const int k = f1(); // OKint n = f2(); // OK}

所以,对于const变量,我们可以要记住一个核心的一点是,const后面的变量是不能当左值的。

往期文章:

FPGA相关:

- Vivado中jobs和threads的区别?选择多个jobs能加快实现速度么?

- SystemVerilog教程之数据类型1

- Vivado中模块封装成edif和dcp

- FPGA 中的有符号数乘法

- 为什么推荐使用XPM?

- RAM IP Core中 Write First Read First和No Change的区别*

- *Vivado调试小结:ILA debug中的数据也许并不可信

- FPGA复位的正确打开方式

- 如何使用Git进行Vivado工程的管理

- 大家一致避免使用的锁存器为什么依然存在于FPGA中?我们对锁存器有什么误解?

- 影响FPGA时序的进位链(Carry Chain), 你用对了么??

- Virtex7 Microblaze下DDR3测试

- Matlab高效编程技巧

- 生成Verilog HDL例化模板

- DCM/DLL/PLL/MMCM区别

其他:

- C++ vector用法详解

- C++ 内联函数 inline的详细分析

- 自动驾驶入门之视觉定位坐标转换

- 什么是噪声温度?-174dBm/Hz又是什么?

FPGA时序约束教程:

- FPGA时序约束理论篇之建立保持时间

FPGA时序约束理论篇之时序路径与时序模型

FPGA时序约束理论篇之IO约束

FPGA时序约束理论篇之时钟周期约束

FPGA时序约束理论篇之两种时序例外

FPGA时序约束理论篇之xdc约束优先级

FPGA时序约束实战篇之梳理时钟树

FPGA时序约束实战篇之主时钟约束

FPGA时序约束实战篇之衍生时钟约束

FPGA时序约束实战篇之延迟约束

FPGA时序约束实战篇之伪路径约束

FPGA时序约束实战篇之多周期路径约束

Vivado时序约束辅助工具

FPGA时序约束之Tcl命令的对象及属性

欢迎关注微信公众号:

加FPGA技术交流群的朋友,请加微信:xhclsys2

还没有评论,来说两句吧...