AMBA基础知识6:AHB-Lite简介

来自:https://www.cnblogs.com/-9-8/p/4737825.html

AHB总线实现了简单的基于burst的传输,数据总线带宽可配置32-1024bit。可以实现简单的fixed pipeline在address/control phase和

data phase之间。

典型的AHB的slave包括:internal memory device,external memory interfaces,high bandwidth peripheral。

AHB必须是对齐传输,word,addr[1:0]为0,half-word,addr[0]为0。包括wrap burst传输,也必须是对齐的。

AHB-Lite协议是整个AHB协议的子集,只支持一个总线主设备,不需要总线仲裁器及相应的总线请求/授权协议,

不支持Retry和Split响应。

AHB-Lite的典型应用结构是一个AHB-Lite master,一些AHB-Lite slaves。slave由APB总线实现,HSEL信号由一个

address decoder产生。从slave到master的rdata,response由一个slave-to-master multiplexor通过选址

送给master。

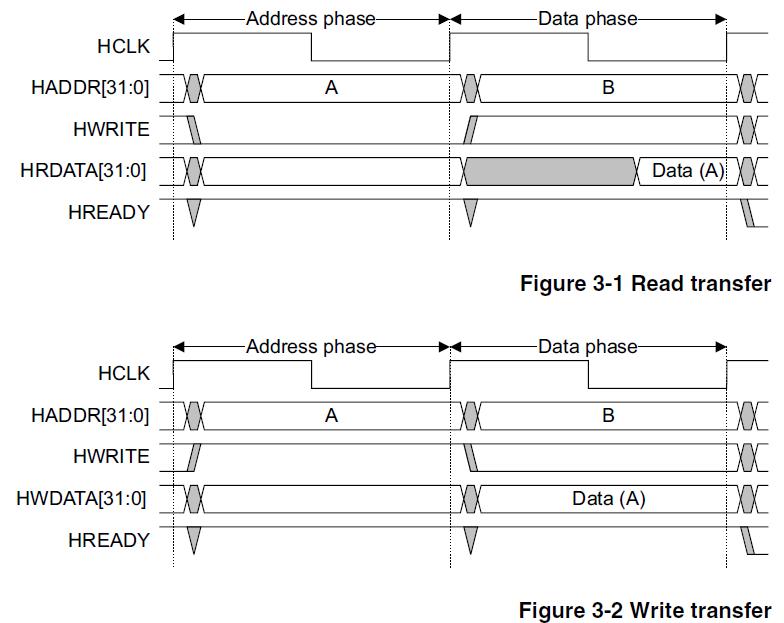

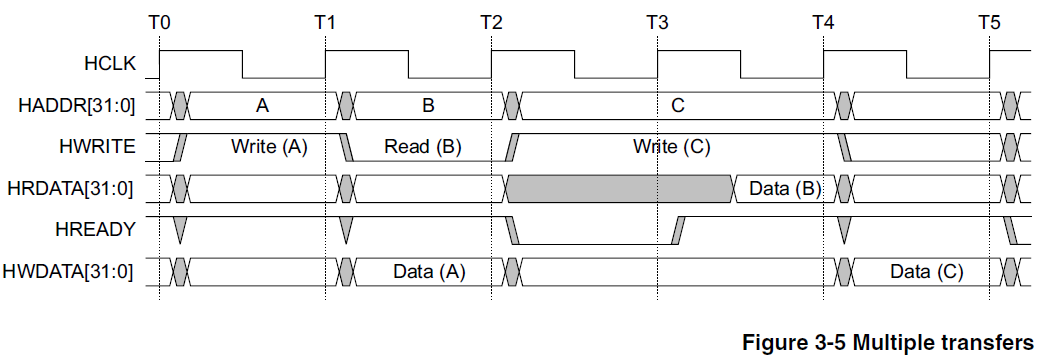

AHB中的transfer由两部分组成,Address phase,Data phase。

slave可以通过信号HREADY来延长data phase,但是不能延长address phase。

在master比较繁忙时,可以通过busy transfer,表示burst还在继续,相当于多延时一个address cycle。

AHB信号大致可以分为五类:

Global signals:HCLK,HRESETn;

Master signals:HADDR,32bit的地址线。

HBURST,3bitde burst长度和类型。支持长度为4/8/16的INCR/WRAP类型的burst。

未定义长度的INCR类型的burst。和Single burst两种新类型。

HMASTLOCK,表示一个locked的transfer,主要用在一个存在多个master访问的slave原语操

作中。因为AHB并不存在乱序操作,所以单一master时,并没用。arm建议,lock transfer之后

加一个IDLE的transfer。

HPROT,4bit包含data/opcode,supervisor/user之外,还包含bufferable,cacheable两位

AHB并没有对secure world的支持。

HSIZE, 3bit表示transfer的带宽,必须小于AHB配置的BUS width。

AHB中的byte lanes由address offset来决定,对于32bit的bus,0x1在小端格

式就只**选择最低的byte。**

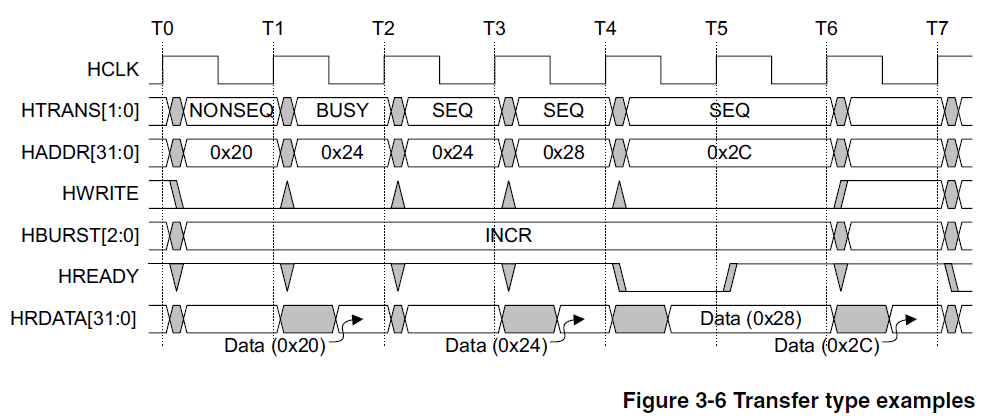

HTRANS,2bit,只有AHB的信号,表示前后两个transfer之间的关系。

IDLE,表示无数据传输,在lock transfer之后以idle结束。slave必须返回OKAY response。

BUSY,允许master在一个transfer中加入idle cycle。并不实现数据的传输,address和control

signals反映在下一个transfer。

NONSEQUENTIAL,表示一个single transfer或者一个burst的第一个transfer。

这个transfer的address和control signal和前一个transfer没关系。

SEQUENTIAL,表示INCR/WRAP类型的transfer。control signal和前一个transfer一样。

address根据前一个transfer计算得到。

AHB的每个transfer的控制是分开的,其中包含burst信息,而AXI的transfer是打包在一个burst中

的。AHB是基于transfer的,AXI是基于burst的。

HWDATA,32bit。

HWRITE,1—write;0—read。

Slave signals:HRDATA,31bit数据,从slave送往Multiplexor。

HREADYOUT,从slave送往Multiplexor表示每个slave自己的READY信号,最终变为HREADY。

HRESP,从slave送往Multiplexor的response信号。

Decode signal:HSEL,从decoder送往slave的HSEL信号,由高位地址线组合逻辑生成。

Multiplexor signals:HRDATA,31bit,从Multiplexor送往master,读数据。

HREADY,从Multiplexor送往master,transfer结束信号。

HRESP,从Multiplexor送往master,response信号。

AHB中的transfer:主要依靠address,data之间的overlapping来实现pipeline。

所以当slave在data phase通过HREADY延长一个 transfer时,下一个transfer的address phase不能被即时

采样,**也会被延长。建议slave插入的wait state不超过16个clk。**

AHB没有enable信号,所以不进行传输时,HTRANS信号有0,表示idle,无数据传输。

只有HTRANS为10,non_seq时,才会开始一个transfer。

AHB中的transfer是不能超过1KB的,不是AXI的4KB。

AHB中要实现一个SEQ的transfer也是NONSEQ起始,然后每次clock rising 采样,其后增加SEQ或BUSY类型

的**transfer,也是每个clock被采样。祥见相册。**

(注意HTRANS[1:0]为BUSY时HRDATA[31:0]不会返回数据)

固定长度的burst,只能自然结束,最后一个seq transfer后,结束。

undefined INCR burst,通过non_seq和idle transfer来进行结束。

不允许通过busy tansfer,来结束burst。

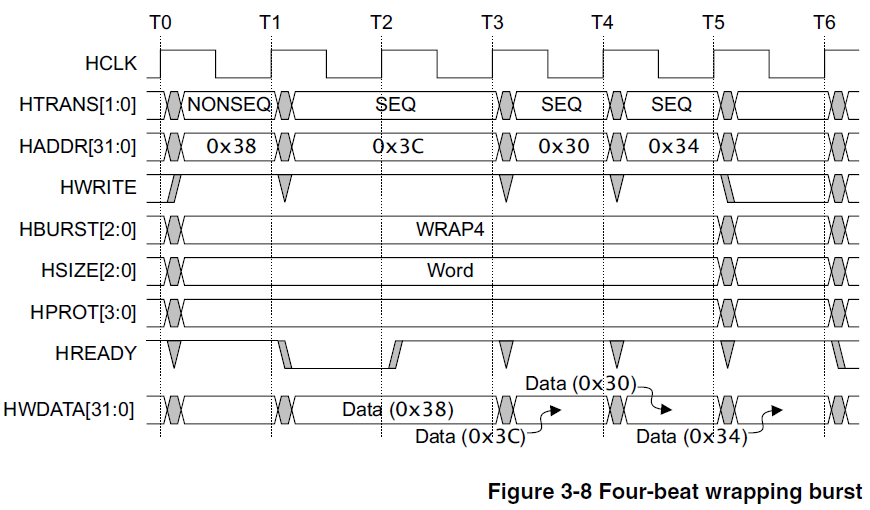

burst中的wrap操作:

AHB的wrap中要求两种对齐:1)字对齐;2)wrap对齐;

Aligned_address = (INT(start_address/number_of_bytes) * number_of_bytes)

Wrap_Boundary = (INT(start_address/number_of_bytes*burst_length) *(number_of_bytes*burst_length))

Address_1 = start_address

Address_n = Aligned_address + (N-1) * number_of_bytes

wrap的边界地址等于burst_length*size的对齐地址,在16byte的对齐,只有低四位变化,每次增加4。

当slave在一个transfer中插入wait state时,下一transfer的可以类型改变,但是会有限制。

1)前一transfer在IDLE类型,这一transfer可以是变为NONSEQ类型;

2)前一transfer在BUSY类型且length固定,这一transfer可以变为SEQ类型;

3)前一transfer在undefined burst length且在BUSY类型,这一transfer可以变为任意类型。

当slave在一个transfer中插入wait state时,在以下情况下可以改变address。

1)当前是一个IDLE类型transfer,address可以改变。

2)当slave返回一个error时,可以在HREADY为低时,改变地址。

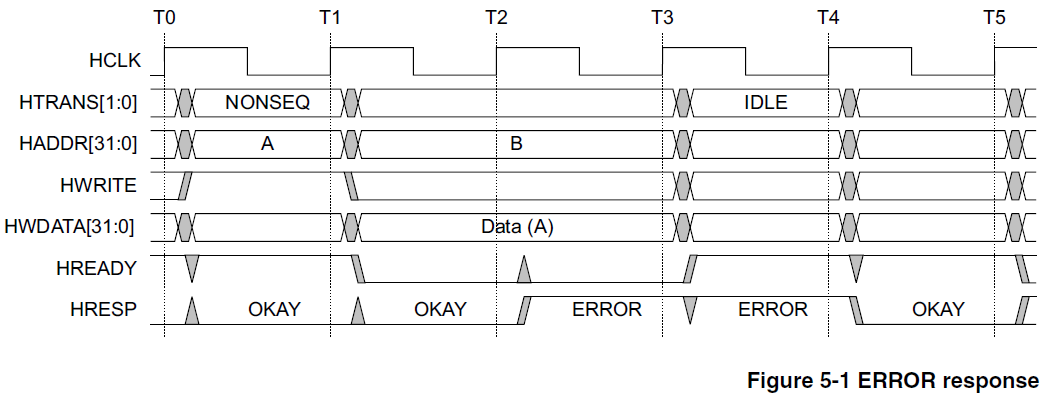

AHB中一个transfer传输的结果:

1) Transfer pending———Hresp=0, Hready=0;

2) Transfer complete———Hresp=0, Hready=1;

3) error response first cycle——-Hresp=1, Hready=0;

4) error response second cycle——Hresp=1, Hready=1;

AHB中的error返回,必须持续两个clock,提前一个cycle可以让master在发出下一个transfer之前,意识到这个transfer的error。

在slave需要更长时间返回resp时,也最多只能有两个cycle的error resp,通过ready进行extend。

一个seq的transfer一般不能超过1K,因为一般IP的地址空间都是以1K为单位的,如果一个transfer超过了IP边界,因为address的值是不变的,所以会导致

第二个IP传输的数据出错,这时应该用NONSEQ重新发起一个新的transfer。

尽管AHB中有wrap类型的传输,但是addr的计算还是master每一个cycle都计算一次的。

还没有评论,来说两句吧...